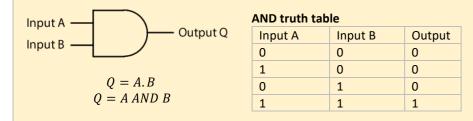

AND gate - has two inputs and will have a true output if the two inputs are true otherwise the output will be false

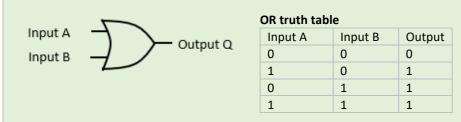

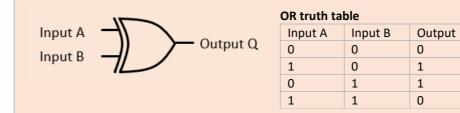

OR gate - has two inputs and will have a true output if either or both the inputs are true

С

NOR gate - has two inputs and will have a true output only if either or both the inputs are false

$Q = \overline{A + B}$ Q = NOT (A + B)

|           | NOR truth table |         |        |  |  |

|-----------|-----------------|---------|--------|--|--|

| Input A   | Input A         | Input B | Output |  |  |

| Input B — | 0               | 0       | 1      |  |  |

|           | 1               | 0       | 0      |  |  |

|           | 0               | 1       | 0      |  |  |

|           | 1               | 1       | 0      |  |  |

NAND gate - has two inputs and will have a true output if either or both the inputs are false

#### $Q = \overline{A.B}$ Q = NOT(A.B)

$Q = A \oplus B$ Q = A X O R B

## **Boolean Identities**

| Commutative laws | A + B = B + A                                    |

|------------------|--------------------------------------------------|

|                  | A.B = B.A                                        |

| Inverse law      | $\bar{A} = A$                                    |

| AND laws         | $A.\bar{A} = 0$                                  |

|                  | A. A = A                                         |

|                  | 0. $A = 0$                                       |

|                  | 1. $A = A$                                       |

| OR laws          | 1 + A = 1                                        |

|                  | 0 + A = A                                        |

|                  | A + A = A                                        |

|                  | $A + \overline{A} = 1$                           |

| Associative laws | (A.B).C = A.(B.C)                                |

|                  | (A+B) + C = A + (B+C)                            |

| Distributive law | A.(B+C) = A.B + A.C                              |

|                  | (A + B). (A + B) = A.A + B.B + A.B + A.B         |

| More identities  | $A + A \cdot B = A$                              |

|                  | $A.\left(A+B\right)=A$                           |

| De Morgan's law  | $\overline{\overline{A}.\ \overline{B}} = A + B$ |

|                  | $\overline{A} + \overline{B} = A.B$              |

Applying De Morgan's Law:

| 1.   | Apply NOT operator the whole expression                                                                          | $\overline{\overline{\bar{A}} . \overline{\bar{B}}} = \overline{A} . \overline{B}$ |

|------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| 2.   | Switch the operator (If the operator is AND switch to OR operator, If the operator is OR switch to AND operator) | $\bar{A}$ + $\bar{B}$                                                              |

| 3.   | NOT the individual terms                                                                                         | A + B                                                                              |

| Orde | er of operation                                                                                                  |                                                                                    |

- 1. Brackets

- 2. NOT

- 3. AND

- 4. OR

- 5. XOR

# Converting a truth table to a logic circuit

There is a general approach to converting a truth table into a logic circuit.

We consider only the lines with an output of 1. We take in the input of each and then AND.

We then OR between each statement such that (NOT A AND B) OR (A AND NOT B). We can then draw the logic circuit.

Worked example: What is the logic circuit for the following truth table

| Input - A | Input - B | Output |

|-----------|-----------|--------|

| 0         | 0         | 0      |

| 1         | 0         | 1      |

| 0         | 1         | 0      |

| 1         | 1         | 1      |

(A AND NOT B) OR (A AND A)

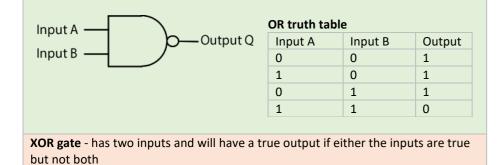

XOR gate

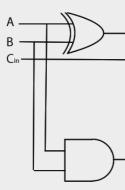

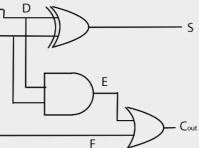

*Full Adder* - A full adder has three bits as inputs one of which is the carry bit. It adds the three bits and outputs two bits the sum (S) and the carry (C). It is made up of an AND, XOR and OR gates

| Α |   | В |   | Cin |   | Cout | 5 | D | E | F |

|---|---|---|---|-----|---|------|---|---|---|---|

| 0 | + | 0 | + | 0   | = | 0    | 0 | 0 | 0 | 0 |

| 0 | + | 0 | + | 1   | = | 0    | 1 | 0 | 0 | 0 |

| 0 | + | 1 | + | 0   | = | 0    | 1 | 1 | 0 | 0 |

| 0 | + | 1 | + | 1   | = | 1    | 0 | 1 | 1 | 0 |

| 1 | + | 0 | + | 0   | = | 0    | 1 | 1 | 0 | 0 |

| 1 | + | 0 | + | 1   | = | 1    | 0 | 1 | 1 | 0 |

| 1 | + | 1 | + | 0   | = | 1    | 0 | 0 | 0 | 1 |

| 1 | + | 1 | + | 1   | = | 1    | 1 | 0 | 0 | 1 |

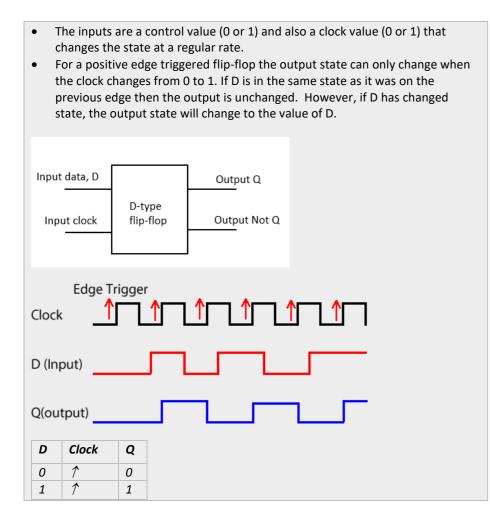

### D-type flip flops

- A flip-flop can store the value of a bit.

- 1 and 0.

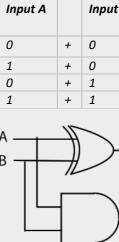

Half adder - A half adder has two bits as inputs (A and B) and adds the two bits and outputs two bits the sum (S) and the carry (C). It is made up of an AND and an

| t B |   | C (carry) | S (sum) |

|-----|---|-----------|---------|

|     | = | 0         | 0       |

|     | = | 0         | 1       |

|     | = | 0         | 1       |

|     | = | 1         | 0       |

D (delay)-type flip flops are used to store one bit and flip between two states: